## ÍNDICE

|                                                                                                    |           |

|----------------------------------------------------------------------------------------------------|-----------|

| <b>1. TÍTULO DEL PROYECTO:</b>                                                                     | <b>1</b>  |

| <b>2. DESCRIPCIÓN DEL PROYECTO:</b>                                                                | <b>1</b>  |

| 3.1. Objetivo general                                                                              | 1         |

| 3.2. Objetivos específicos                                                                         | 1         |

| <b>3. MÉTODOS E INSTRUMENTOS UTILIZADOS</b>                                                        | <b>2</b>  |

| <b>4. DESARROLLO DEL TRABAJO</b>                                                                   | <b>3</b>  |

| 4.1. DISEÑO DEL HARDWARE DE MEDICIÓN                                                               | 3         |

| 4.2. DISEÑO PCB                                                                                    | 8         |

| 4.3. FABRICACIÓN DE PCB                                                                            | 10        |

| 4.4 GABINETE DE SIPM                                                                               | 11        |

| 4.5 DESARROLLO DE HDL                                                                              | 12        |

| 4.6 DESARROLLO DE APLICACIÓN                                                                       | 14        |

| <b>5. RESULTADOS OBTENIDOS</b>                                                                     | <b>15</b> |

| 5.1. PRUEBA DE IRRADIACIÓN                                                                         | 15        |

| 5.2. PRESENTACIÓN EN CONGRESO                                                                      | 17        |

| <b>6. VALORACIÓN DE DIFICULTADES Y ELEMENTOS FACILITADORES PARA LA CONCRECIÓN DE LA ACTIVIDAD:</b> | <b>18</b> |

| <b>7. CONCLUSIONES:</b>                                                                            | <b>18</b> |

| <b>8.BIBLIOGRAFÍA</b>                                                                              | <b>19</b> |

## 1. TÍTULO DEL PROYECTO:

Banco de pruebas de SiPMs para su caracterización en ensayos de tolerancia a radiación

## 2. DESCRIPCIÓN DEL PROYECTO:

### 3.1. Objetivo general

Se realizó el diseño y construcción de un banco de pruebas de fotomultiplicadores de silicio (SiPM) que permite la caracterización del ruido en oscuridad (dark-count rate), el espectro single-photoelectron (SPE), el consumo de corriente del dispositivo y la ganancia. El sistema es portable, económico y tiene la capacidad de realizar la caracterización del SiPM a una distancia de 2m, permitiendo la realización de ensayos de tolerancia a radiación sin la exposición innecesaria del banco de pruebas.

### 3.2. Objetivos específicos

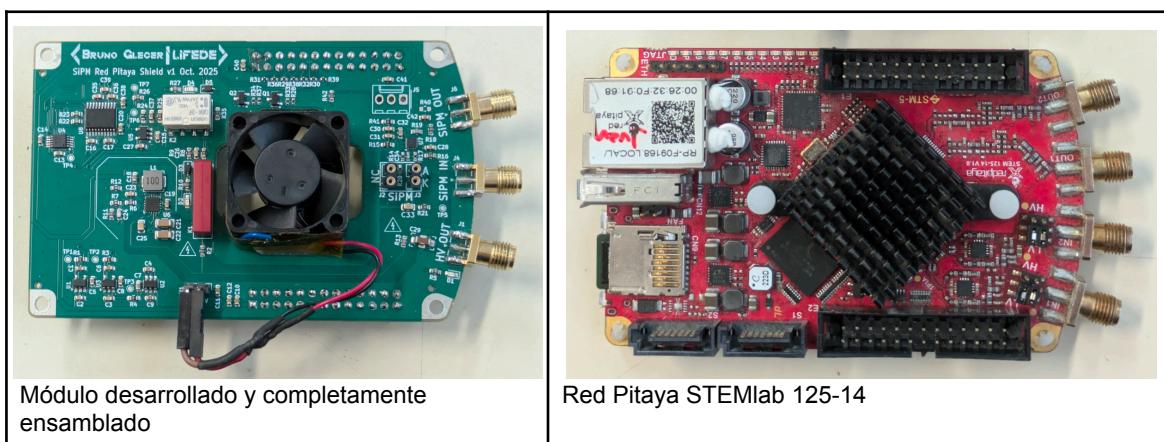

Se diseñó y fabricó un módulo que se acopla directamente a la parte superior de una *Red Pitaya STEMlab 125-14* [1], una computadora de placa única con un FPGA integrado y front-end analógico de alta velocidad con dos ADCs y dos DACs de 125 MSps. El módulo desarrollado sirve para la alimentación del SiPM en un rango de 10 V a 80 V, posee capacidades de monitoreo de corriente de entre 1 nA y 100  $\mu$ A y cuenta con un preamplificador de alta velocidad para el acondicionamiento de la señal previo a la digitalización por la Red Pitaya.

### 3. MÉTODOS E INSTRUMENTOS UTILIZADOS

Para la adquisición de las señales de alta velocidad generadas por el SiPM se utilizó la computadora de placa Red Pitaya, esta posee un front-end analógico con dos entradas y dos salidas de alta velocidad (125 MSpS) conectadas a un FPGA Xilinx Zynq-7000 que permite el procesamiento de las señales en tiempo real y la comunicación con un procesador físico integrado ARM con capacidades de ejecutar un sistema operativo basado en Linux.

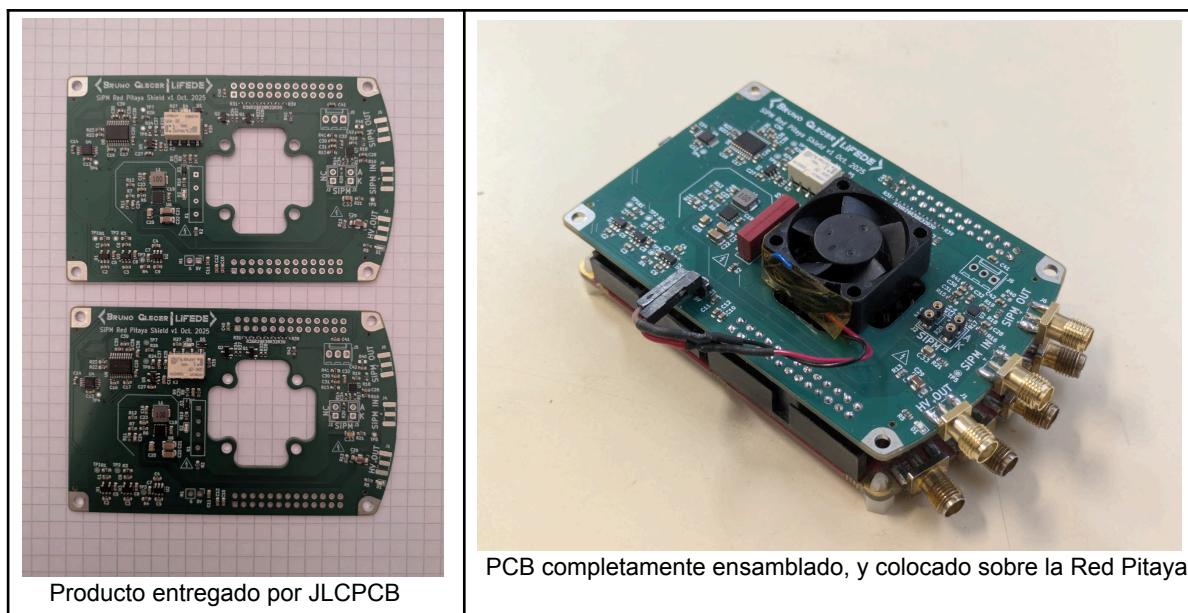

El diseño del módulo de pruebas de SiPM fue realizado en KiCAD[2] y fabricado en JLCPCB [3]. El fabricante realizó el ensamblado de los componentes de montaje superficial (SMD), mientras que los componentes de agujeros pasantes (THT) fueron adquiridos de DigiKey [4] y montados manualmente.

Como sistema operativo base para la Red Pitaya se optó por utilizar una versión modificada de Debian Linux desarrollada por Demin Pavel [5] que cuenta con los drivers y el device-tree necesarios para su funcionamiento.

El software de aplicación fue desarrollado en el lenguaje C, utilizando la misma Red Pitaya como plataforma para compilar los programas. El desarrollo se realizó a través de una conexión SSH con el editor de texto Visual Studio Code.

La implementación en la FPGA para el procesamiento de señales fue diseñada usando el entorno de desarrollo Vivado de AMD versión 2025.1 [6]. Se utilizó una combinación de código en Verilog, módulos provistos por el fabricante y las conexiones de alto nivel fueron realizadas en el entorno de diseño por bloques.

Para facilitar el desarrollo del sistema de procesamiento digital se usó un entorno de Python junto con librerías como SciPy, NumPy y Matplotlib para realizar pruebas del funcionamiento previo a su implementación en FPGA, en especial del sistema de detección de picos.

Para el procesamiento posterior de los datos se utilizó Python. El posprocesamiento incluye correcciones necesarias para la visualización correcta de los datos.

## 4. DESARROLLO DEL TRABAJO

### 4.1. DISEÑO DEL HARDWARE DE MEDICIÓN

El módulo desarrollado debe ser capaz de proveer la tensión de alimentación para el SiPM, medir el consumo de corriente y realizar la preamplificación de la señal del SiPM. A continuación se muestran las distintas secciones del circuito que dan lugar a estas funcionalidades.

#### POLARIZACIÓN

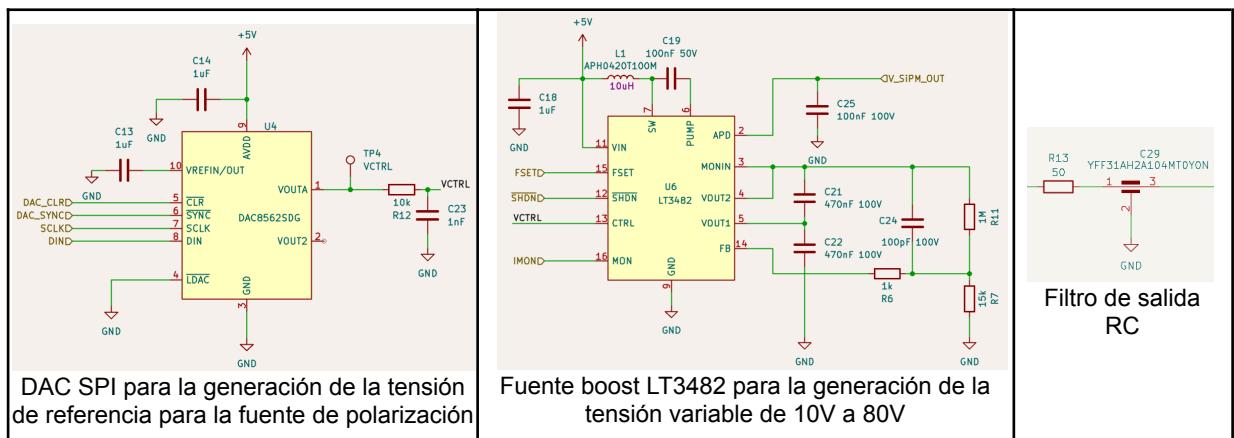

Para la generación de la tensión de polarización, se utilizó el circuito integrado LT3482 [7], este IC es un controlador de fuente conmutada tipo boost que permite alcanzar hasta 90 V en su salida (80V si se usa la funcionalidad de medición de corriente). Está específicamente diseñado para la polarización de fotodiodos avalanche, un tipo de fotodetector muy relacionado al SiPM.

Esta fuente permite regular su tensión de salida mediante el ajuste de su tensión de referencia a través de un pin de control (CTRL). Esta tensión es fijada por un DAC de 16-bit (DAC8562 [8]) controlado por SPI desde la Red Pitaya.

Para minimizar el ruido de conmutación presente en la salida, se utilizó un filtro pasa-bajos RC implementado usando un capacitor del tipo feedthrough para minimizar inductancias parásitas.

## SENSADO DE CORRIENTE

Para la medición del consumo de corriente del SiPM se aprovechó el espejo de corriente integrado en la fuente LT3482 que espeja la corriente consumida por el SiPM sobre el pin MON, con una relación 5:1.

El rango de medición deseado para el SiPM es de 1 nA a 100  $\mu$ A, es decir, que la medición de corriente del pin MON debe ser entre 200 pA a 20  $\mu$ A. Esto presenta un desafío debido a los niveles muy bajos de corriente que deben ser medidos.

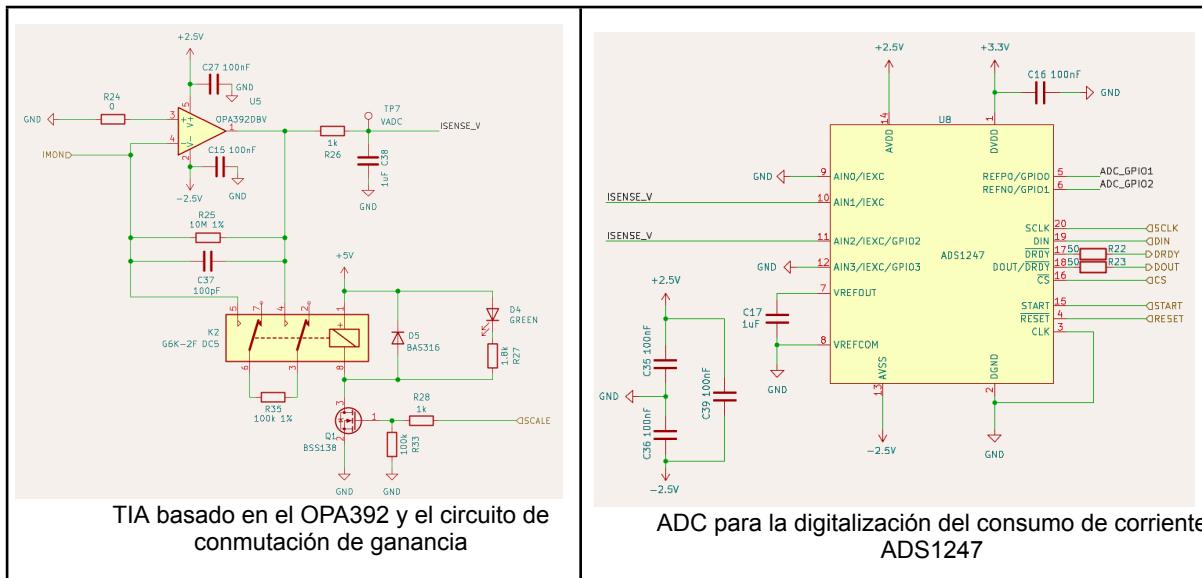

Para poder digitalizar la señal, primero debe ser convertida a una señal proporcional de tensión, para esto típicamente se utiliza una resistencia, pero debido a los valores de corrientes muy bajos, esto puede interferir con las corrientes de fuga en la entrada del ADC. Para evitar esto, se utilizó un amplificador de transimpedancia (TIA) basado en el amplificador operacional OPA392 [9] que tiene muy buenas características de corrientes de fuga ( $\sim 10$  fA), ruido, y offset (10  $\mu$ V).

Para lograr el rango dinámico de 100.000 veces (100  $\mu$ A / 1 nA), es necesario commutar la ganancia del TIA, pero para minimizar la cantidad de configuraciones de ganancia distintas, se utilizó un ADC de alta resolución (24bit), permitiendo el uso de solamente dos valores de ganancia, 10M $\Omega$  y 100k $\Omega$ . Esta commutación se logra con un relé de señal.

| $I_{SiPM}$  | Ganancia      | $V_{ADC}$ |

|-------------|---------------|-----------|

| 1nA         | 10M $\Omega$  | 2mV       |

| 1 $\mu$ A   | 10M $\Omega$  | 2V        |

| 1 $\mu$ A   | 100k $\Omega$ | 20mV      |

| 100 $\mu$ A | 100k $\Omega$ | 2V        |

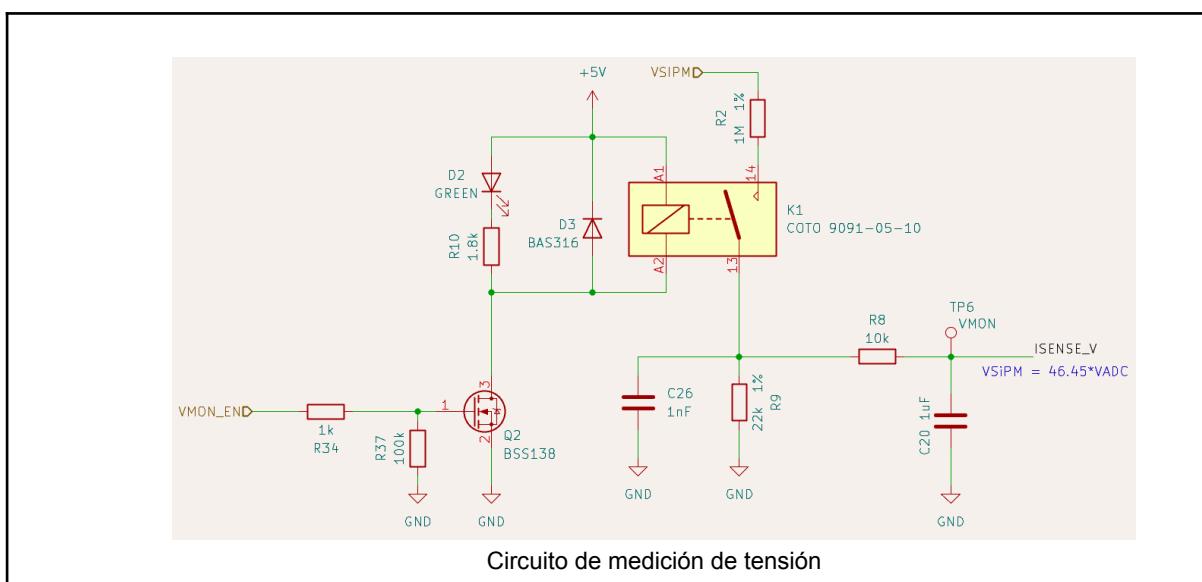

## SENSADO DE TENSIÓN

Debido a que la fuente no tiene la capacidad de controlar con precisión la tensión de polarización en la salida, es necesario realizar la medición de la misma. Esto trae el problema que realizar una medición de la tensión de polarización (que puede alcanzar hasta una tensión de 80V) con un divisor resistivo, cargaría demasiado la salida, afectando la medición de corriente. Para evitar esto, se utilizó un relé de alta resistencia de aislamiento para conectar y desconectar el divisor. Cuando se desea realizar una medición de tensión de polarización, se cierra el relé, afectando la medición de corriente, pero permitiendo la medición tensión. La salida del divisor resistivo es leída por el mismo ADC que digitaliza la señal de medición de corriente.

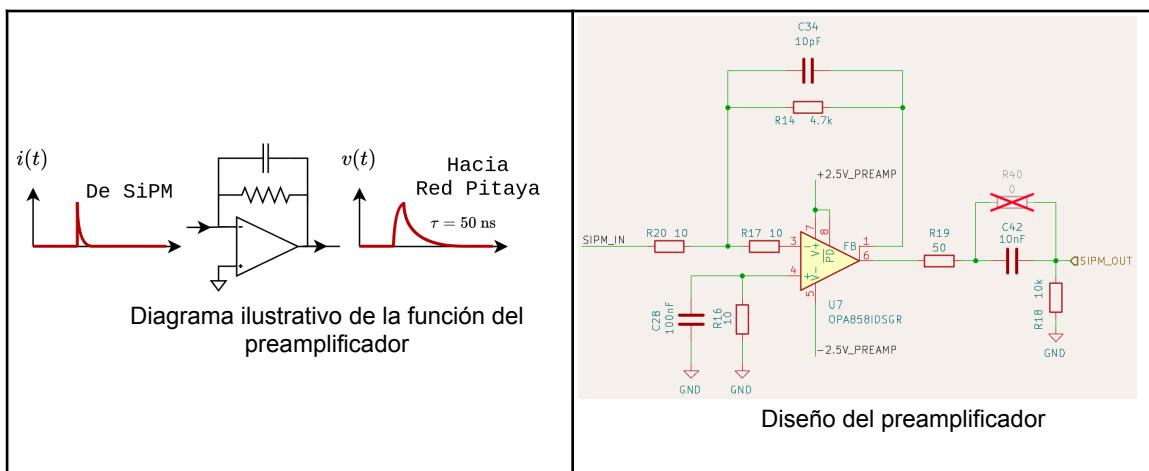

## PREAMPLIFICADOR

El módulo diseñado cuenta con un preamplificador de carga que permite el acondicionamiento de la señal del SiPM previo a la adquisición por la Red Pitaya. Este amplificador cuenta con dos funciones: Primero, convertir la señal de corriente del SiPM en una señal de tensión usando cierto valor de ganancia de transimpedancia, y segundo, integrar la señal para extender su duración en el tiempo. Esto último es necesario debido a que la mayoría de los SiPM tienen capacitancias de salida muy bajas y por lo tanto pulsos de duración muy cortos ( $< 100$  ns), esto normalmente es deseable en aplicaciones de alta resolución temporal, pero debido a la frecuencia de muestreo limitada de la Red Pitaya de 125 MSpS, pulsos de menos de 160 ns (20 muestras) pueden ser muy rápidas para ser medidas correctamente, por lo tanto es deseable capturar el pulso con un integrador de carga que retenga la señal por un tiempo aceptable. En este caso se diseñó con una constante de tiempo  $\tau = 47$  ns, por lo tanto, las señales leídas por la red pitaya, tienen una duración de alrededor de  $4\tau = 190$  ns = 23 muestras.

Para el amplificador se utilizó un amplificador operacional OPA858 [9], este modelo es específico para ser utilizado como TIA para aplicaciones de fotodetectores.

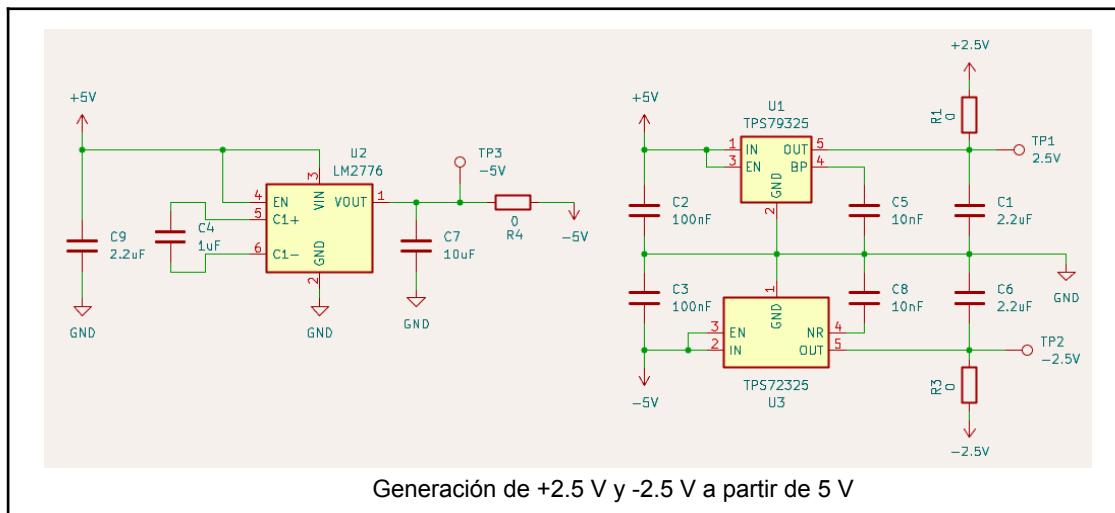

## ALIMENTACIÓN

Muchos de los componentes requieren de tensiones especiales para operar correctamente, en particular el ADS1247, OPA392 y OPA858 requieren de alimentación de  $\pm 2.5$  V y de bajo ruido. Para generar estas tensiones se utilizó el LM2776 para invertir la tensión de 5 V provista por la Red Pitaya a -5 V. Luego se utilizó el TPS72325 para producir una tensión

de -2.5 V a partir de los -5 V, y un TPS79325 para producir +2.5 V a partir de los +5 V originales. Los tres componentes fueron elegidos debido a su bajo nivel de ruido.

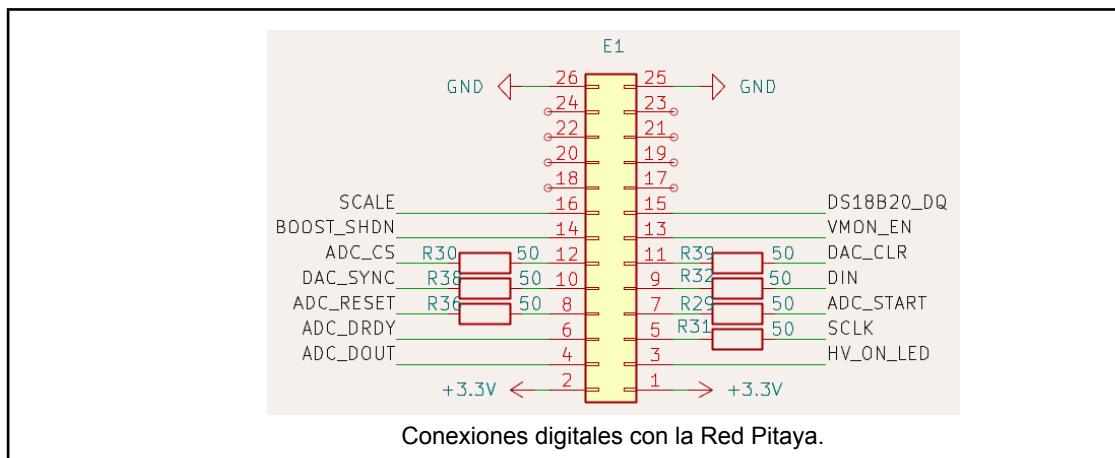

### COMUNICACIÓN ON RED PITAYA

La interfaz digital del módulo desarrollado con la Red Pitaya consiste de una comunicación SPI, dos señales digitales para comandar los relés de cambio de escala y medición de tensión (señales SCALE y VMON\_EN respectivamente), señal de apagado de la fuente de polarización (BOOST\_SHDN), y la señal para controlar un led indicador de tensión de polarización encendida (HV\_ON\_LED). Además, el módulo cuenta con un puerto para la conexión de un sensor de temperatura one-wire DS18B20, que no se encuentra utilizado actualmente.

Todas estas señales se conectan a pines de IO de la lógica programable (PL). A pesar de que el Zynq-7000 cuenta con pines SPI con interfaz directa al CPU, se optó por realizar las conexiones a la PL para obtener mayor flexibilidad de configuración de ser necesario.

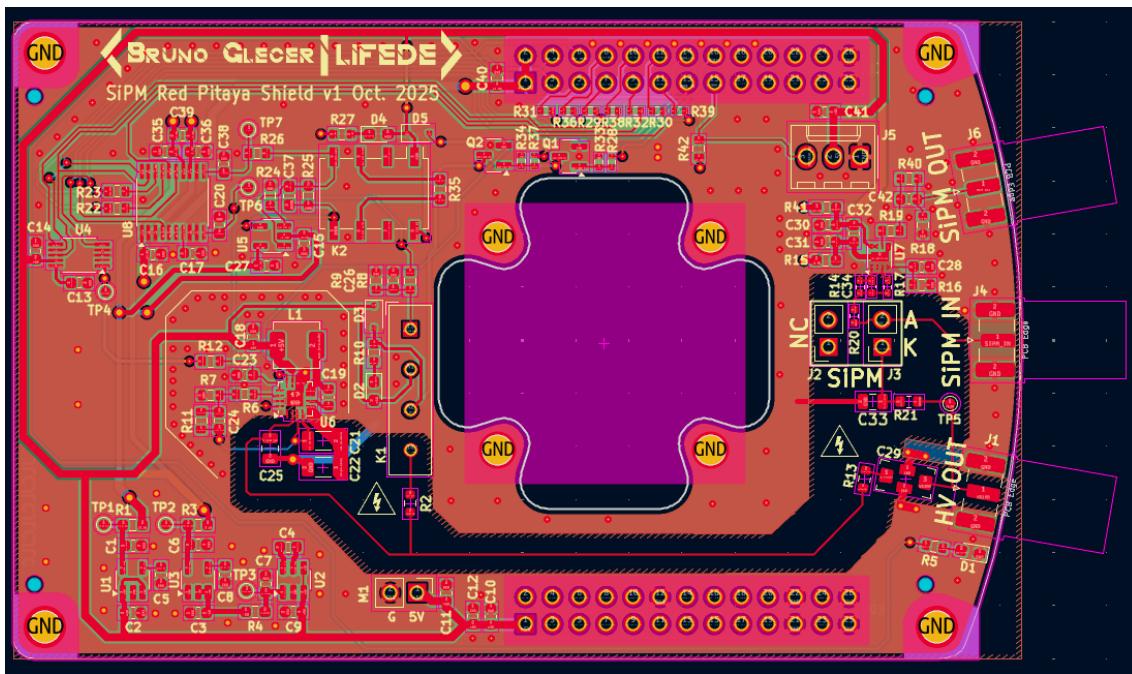

## 4.2. DISEÑO PCB

El PCB fue diseñado en KiCAD, usando la librería de componentes integrada y algunos diseños de esquemático y footprint propios. Se realizó un diseño de 4 capas debido a la densidad de señales y mejores conexiones a masa. El stack up es el siguiente:

|         |                                                      |

|---------|------------------------------------------------------|

| Top     | Plano GND, señales y componentes                     |

| Inner 1 | Exclusivamente plano GND                             |

| Inner 2 | Plano GND, señales sensibles y señales de bajo dv/dt |

| Bottom  | Plano GND, señales y conectores de Red Pitaya        |

Para el diseño del PCB se tuvieron que tener en cuenta muchas consideraciones. A continuación se explican algunas de las más importantes:

1. **Compatibilidad con Red Pitaya:** Para optimizar la portabilidad del sistema, a lo posible, el contorno del PCB debe ser idéntico al de la Red Pitaya. Usando un modelo 3D STEP oficial de la Red Pitaya como referencia [10], se diseñó el contorno del PCB, se ubicaron los conectores header de 2x13 y agujeros de montaje en las mismas posiciones que la placa de la Red Pitaya.

2. **Ventilación:** El Zynq-7000 en la Red Pitaya disipa una cantidad de calor considerable, si bien la Red Pitaya cuenta con un disipador, este no es suficiente si se encuentra obstruido como en el caso de que se le coloque algo encima de él. Para mejorar el enfriamiento del Zynq-7000 se reservó el espacio central del PCB para colocar un agujero que deja descubierto la gran mayoría del área ocupada por el disipador del procesador, y se colocó un ventilador de 25x25 mm sobre este espacio.

3. **Interferencia de fuente boost:** La fuente boost LT3482 al ser una fuente conmutada es posible que por interferencia conducida e irradiada inserte ruido en señales sensibles como ser las de medición de corriente o las señales de alta velocidad del SiPM. Para minimizar esto, la fuente fue ubicada lejos del preamplificador de alta velocidad, y todo su circuito fue encerrado por vía stitching.

4. **Corriente de fuga en la tensión de polarización:** La tensión de polarización puede alcanzar los 80 V, y se desea mantener las corrientes de fuga por debajo de 1 nA para mantener lecturas precisas del consumo de corriente. Si bien es muy difícil predecir los niveles de corrientes de fuga por la resistencia finita entre la tensión y la masa, existen consideraciones que se pueden tomar para minimizarla. Una de ellas es mantener la mayor distancia posible entre la tensión y los planos de masa. Aunque no resulte posible mantener una distancia mínima muy grande en todas las áreas, es buena práctica intentar minimizar la cercanía en la mayor cantidad del recorrido posible. Esta medida se puede ver en el diseño en la parte inferior del PCB donde se observa la distancia entre la traza de la tensión de polarización, el plano de masa en la capa superior, y la ausencia de planos de masa por debajo de la traza.

5. **Protección de señales de bajo nivel:** La señal de monitoreo de corriente de la fuente LT3482 transporta niveles de corriente por debajo del 1 nA. Esto lo hace muy sensible a fugas de corriente con conductores que estén a tensiones distintas y a señales con dv/dt elevados. Para proteger lo más posible esta señal, la gran mayoría de la traza fue pasada por una capa interna del PCB, completamente rodeada de planos de masa.

6. **Resistencias para limitar dv/dt en SPI:** La comunicación SPI de la Red Pitaya con los componentes es una fuente potencial de ruido debido a cambios rápidos en las tensiones de las señales digitales. Esto se puede limitar colocando resistencias en serie cerca del pin de salida de cada señal. Se usaron resistencias de  $50\Omega$ .

El diseño completo, incluyendo archivos de proyecto, esquemáticos, lista de componentes y archivos de fabricación se encuentran en el repositorio del proyecto [11].

#### 4.3. FABRICACIÓN DE PCB

El diseño fue enviado a JLCPCB para su fabricación. Se ordenaron 5 unidades, 2 de las cuales fueron ensambladas con los componentes SMD provistos por el fabricante. Los componentes restantes fueron ordenados del distribuidor de componentes DigiKey.

A continuación se muestran algunas de las características de fabricación del PCB. Los costos no incluyen envíos ni impuestos.

| Parámetros de fabricación de PCB |                    | PCB + SMD: JLCPCB          |                   |

|----------------------------------|--------------------|----------------------------|-------------------|

| Cantidad de PCBs                 | 5                  | Fabricación PCB (5u)       | USD 8.00          |

| Cantidad de PCBs Ensamblados     | 2                  | Ensamblaje PCB (2u)        | USD 92.36         |

| Color de Solder Mask             | Verde              | <b>Total</b>               | <b>USD 100.36</b> |

| Grosor de PCB                    | 1.6mm              | <b>Total/BOM</b>           | <b>USD 47.78</b>  |

| Grosor de Cobre Externo          | 1 oz (35 µm)       | Componentes THT: DigiKey   |                   |

| Grosor de Cobre Interno          | 0.5 oz (17 µm)     | <b>Total/BOM</b>           | <b>USD 26.72</b>  |

| Terminación                      | HASL con Pb        | <b>Costo Final por PCB</b> |                   |

| Tamaño mínimo de agujero         | 0.3mm/(0.4/0.45mm) | <b>USD 74.50</b>           |                   |

| Variedad de componentes          | 43                 |                            |                   |

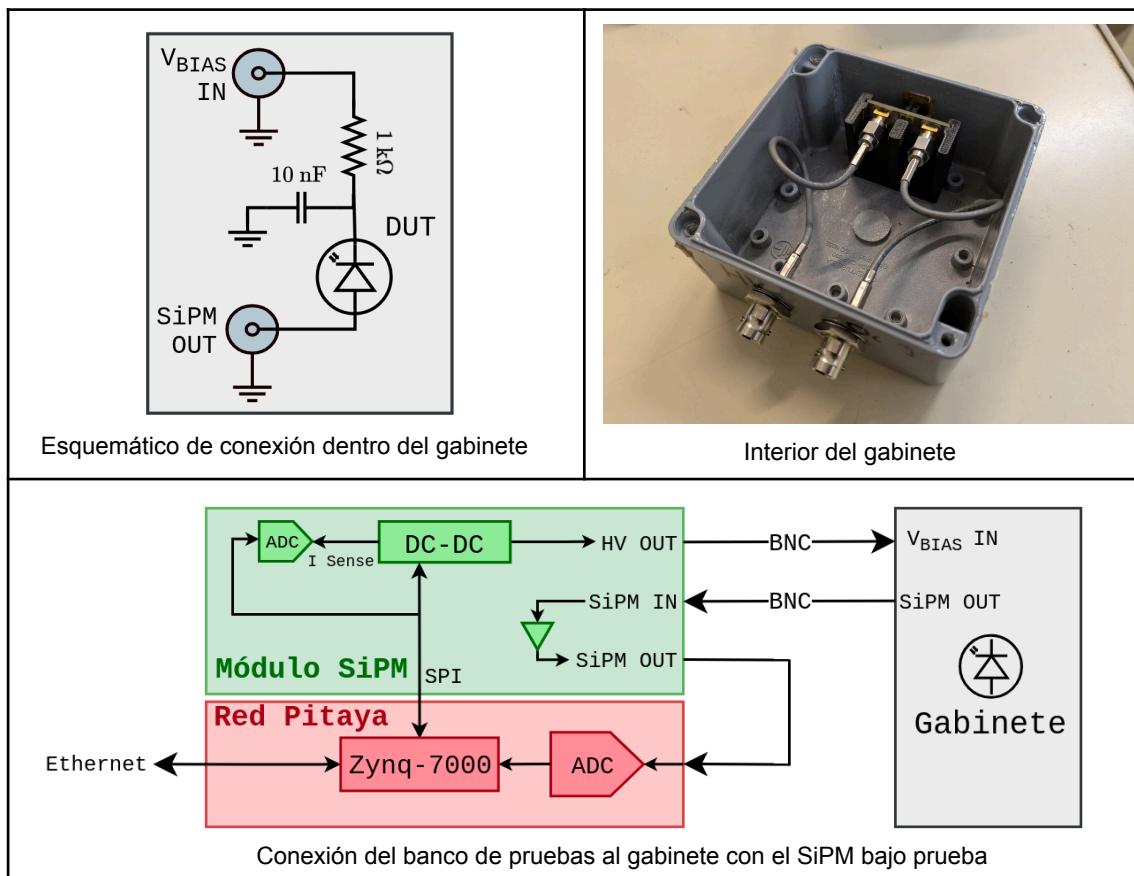

#### 4.4 GABINETE DE SiPM

Es conveniente colocar el SiPM a irradiar dentro de un gabinete fácil de manipular. Esto le brinda protección al SiPM contra interferencia electromagnética, golpes y además sirve de soporte para colocar en la instalación donde se realiza la irradiación.

El gabinete diseñado para el SiPM cuenta con un PCB donde se puede montar el dispositivo, junto con un filtro RC en la alimentación. Para las conexiones del gabinete se utilizaron conectores BNC debido a su robustez y facilidad de operar.

Es importante notar que el material del gabinete debe ser cuidadosamente elegido en base al tipo de radiación utilizado. Este gabinete fue diseñado para ser usado en irradiaciones con neutrones rápidos y rayos gamma, que tienen una sección de interacción muy chica con el aluminio.

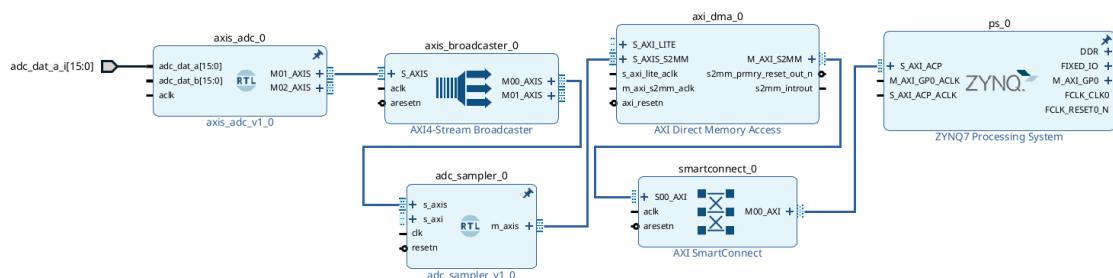

## 4.5 DESARROLLO DE HDL

El FPGA es responsable del procesamiento en tiempo real de las señales del SiPM. La lógica implementada debe ser capaz de realizar todas las tareas necesarias con los datos provenientes del ADC. A continuación se explican los distintos sistemas implementados.

### 4.5.1 Escritura de Señal en Memoria

Si bien no fue especificado anteriormente, una funcionalidad básica del sistema es capturar por un periodo de tiempo la señal del SiPM y guardarla para luego analizarla manualmente. Esto es útil para verificar que las mediciones son válidas, además de permitir otros tipos de análisis sobre la señal. Se determinó que un tiempo apropiado de adquisición es 10 ms ( $1.25 \cdot 10^6$  muestras). Con un dark-rate típico de 50 kcps esto equivale a 500 pulsos de ruido térmico adquiridos en promedio.

Para escribir las  $1.25 \cdot 10^6$  muestras en memoria, se utilizó el IP (Propiedad Intelectual) de DMA (Direct Memory Access) ofrecido por Vivado. La forma en la que se utilizó este IP recibe una serie de datos por una interfaz AXI-Stream y los escribe en forma secuencial en una región de memoria RAM. Además, el módulo cuenta con una interfaz de configuración AXI-Lite que permite su configuración.

Para el correcto funcionamiento, el IP espera una señal de finalización por la entrada de AXI-Stream, la cual debe ser proporcionada manualmente. Para lograr esto se desarrolló el módulo *adc\_sampler.v* que puede ser configurado por AXI-Lite para enviar la cantidad de muestras deseadas al DMA incluyendo la señal de finalización.

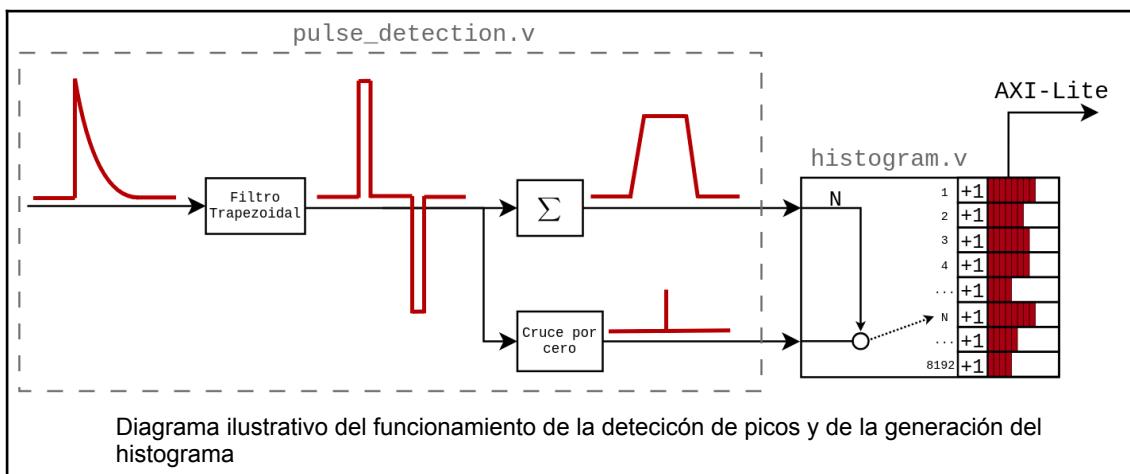

### 4.5.2 Detección de Picos y Generación de Histograma

Para generar el espectro o histograma de amplitudes de pulsos, la señal debe ser analizada en tiempo real para la detección de picos, esto se realiza mediante el uso de un filtro trapezoidal [12]. El filtro produce una señal en forma de trapezoide por cada pulso exponencial que recibe. El beneficio de este filtro es que sirve de buen estimador de la altura

del pulso, con alto rechazo al ruido. Cuando ocurre la detección de un pulso, se incrementa en uno un contador dependiendo del valor de la altura del trapecio en ese instante. Esto permite producir en memoria el espectro de las alturas de los pulsos que se reciben del SiPM. La memoria usada en histogram.v es BRAM.

#### 4.5.3 Comunicación SPI

Para la comunicación SPI con el ADS1247 y DAC8562 se utilizó el IP *AXI Quad SPI*. Este IP permite la comunicación con dispositivos SPI externos al FPGA. La comunicación del procesador con el IP se realiza mediante AXI-Lite. La frecuencia de clock del SPI utilizada es de aproximadamente 1 MHz.

#### 4.5.3 GPIO

Para el manejo de las señales de GPIO (BOOST\_SHDN, SCALE, VMON\_EN) se utilizó el IP *AXI GPIO* que permite controlar señales digitales mediante registros accesibles por una interfaz AXI-Lite.

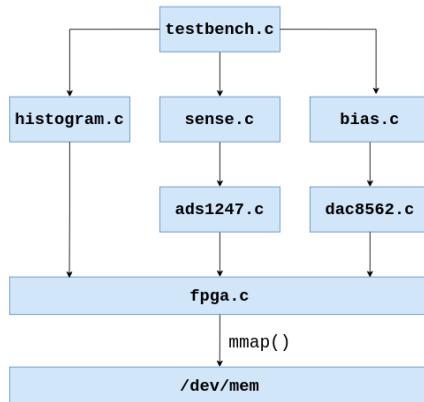

#### 4.6 DESARROLLO DE APLICACIÓN

El código ejecutado en el procesador sobre el sistema Linux es responsable de las siguientes tareas:

1. Inicialización y configuración de módulos en el FPGA (SPI, filtro, histograma y DMA)

2. Inicialización y configuración del ADS1247 y DAC8562

3. Control de rango de lectura, selección entre medición de tensión o corriente y habilitación de fuente DC-DC (SCALE, VMON\_EN, BOOST\_SHDN) mediante GPIO

4. Ajuste de tensión de polarización mediante el DAC8562

5. Lectura de corriente y tensión de polarización mediante el ADS1247

6. Lectura de memoria dedicada a DMA para la lectura de señales

7. Lectura del histograma almacenado en BRAM.

8. Lectura periódica de todas las mediciones (señal, histograma, corriente, curva IV)

9. Almacenamiento de datos en memoria no volátil.

El programa fue implementado en el lenguaje C. La capa más alta del programa consiste de una máquina de estados que realiza las distintas mediciones periódicamente, cada mediciones con un intervalo de tiempo diferente. Las capas más bajas consisten de funciones para la lectura y escritura de registros del hardware, acceso a memoria física para la comunicación con el FPGA, entre otras funciones que exceden el alcance de este informe

## 5. RESULTADOS OBTENIDOS

### 5.1. PRUEBA DE IRRADIACIÓN

Del 7 de noviembre de 2025 al 11 de noviembre de 2025 se realizó una campaña de irradiación en el recinto del Reactor Argentino 1 (RA1) del Centro Atómico Constituyentes donde se irradió un SiPM del fabricante Hamamatsu, modelo S12571-100C [13]. Se utilizó una fuente de AmBe con una actividad de 5 Ci a una distancia de 5 cm.

Durante la irradiación se realizaron mediciones utilizando el banco de pruebas desarrollado. La configuración es la siguiente:

|                          |             |                         |           |

|--------------------------|-------------|-------------------------|-----------|

| Curve IV                 | 20 minutos  | Tensión de polarización | 66V       |

| Traza de señal de 10ms   | 10 minutos  | Curva IV                | 61V a 69V |

| Histograma de 3 segundos | 1 minuto    |                         |           |

| Consumo de corriente     | 10 segundos |                         |           |

A continuación se muestran algunos resultados obtenidos de las mediciones. Estos resultados no abarcan todas las datos obtenidos, pero sirven para la demostración del correcto funcionamiento del banco de pruebas.

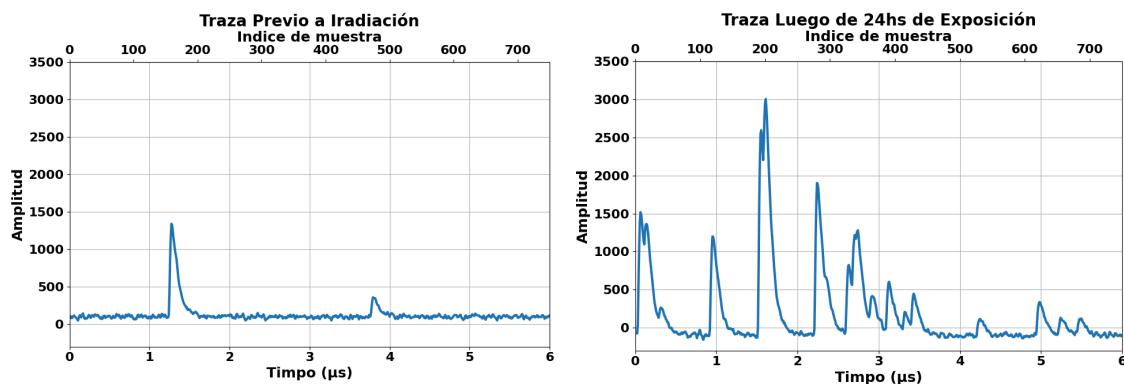

#### 5.1.1 Trazas de Señales

Como se puede ver en los siguientes gráficos, el SiPM luego de 24 horas de exposición a radiación presenta un nivel de ruido mucho mayor que previo a la irradiación.

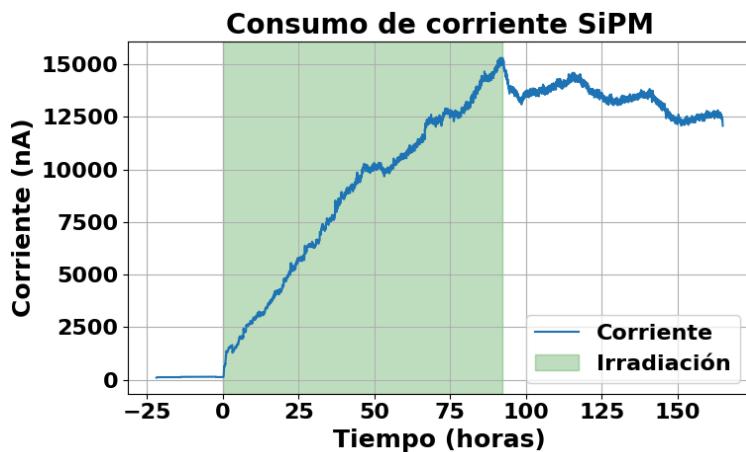

### 5.1.2 Corriente en Oscuridad

A continuación se puede observar el consumo de corriente del SiPM en oscuridad. Se observó un incremento de 100 veces la corriente de oscuridad en el plazo de 92 horas. Una vez retirada la fuente, se puede observar como la corriente deja de incrementar.

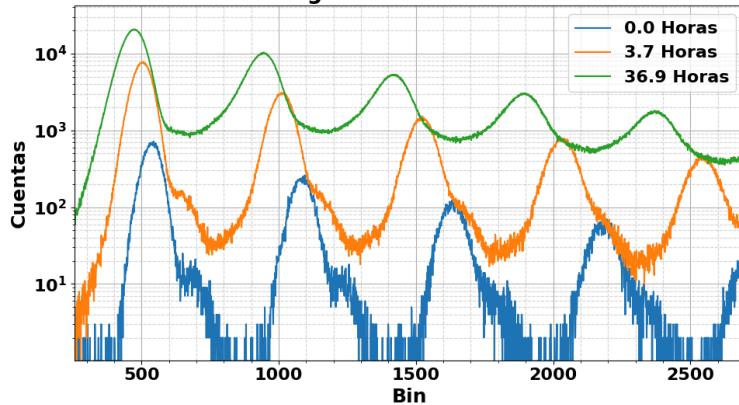

### 5.1.3 Histograma de eventos

En la siguiente figura se visualizan tres histogramas capturados en distintos momentos de la irradiación. Como es de esperar, se puede observar la típica distribución de amplitudes característico de un SiPM. El desplazamiento hacia arriba del histograma indica el aumento del dark-rate, mientras que la disminución entre el pico del histograma y la base, muestra una reducción de la resolución energética de las mediciones del SiPM en forma en el aumento de la dispersión de la ganancia.

### Histogramas seleccionados

## 5.2. PRESENTACIÓN EN CONGRESO

Este trabajo fue presentado en forma de póster en el V Congreso Argentino de Técnicas Neutrónicas [14] realizado en UTN FRBA el 18 y 19 de noviembre de 2025.

**Banco de Pruebas Portable para la Caracterización de SiPMs en Ensayos de Irradiación Basado en FPGA**

UTN-BA | IIAHIN-CONICET | Red Playa | CNEA | CONICET | Bruno Glecer<sup>1</sup>, Julián Franco Grossi<sup>2</sup>, Aníbal Dayan<sup>3</sup>, Ricardo Darío Reñiz<sup>4</sup>, Matías Bergmann<sup>5</sup>, Agustín Lucero<sup>6</sup>, Federico Suárez<sup>7,8</sup>

<sup>1</sup>UTN-FRBA | <sup>2</sup>IIAHIN-CNEA | <sup>3</sup>CNEA | <sup>4</sup>Red Playa | <sup>5</sup>CONICET | <sup>6</sup>CONICET | <sup>7</sup>UTN-FRBA | <sup>8</sup>CONICET

**INTRODUCCIÓN**

Los SiPM son dispositivos sensibles a daños por radiación [1], por lo que demandan ser ensayados por su tolerancia a la radiación de alta energía y sus aplicaciones especiales. Estos ensayos se realizan en instalaciones especializadas y dedicadas a la radiación de componentes y materiales.

Debido a esta necesidad, es importante el desarrollo de un sistema de caracterización fácil de transportar y estable de razonable costo para probar la respuesta de los SiPMs en la exposición innecesaria de la electrónica de instrumentación.

Además, el mismo sistema debe suministrar la tensión de polarización del fotodetector. Esta debe ser suministrada hasta 80V y de muy bajo ruido como para no interferir con las señales de respuesta de los SiPMs.

• Adquisición de señales a 125 MSps

• Detección de picos y generación de histograma en tiempo real

• Polarización de SiPMs

• Monitorizado de corriente

• Implementación en FPGA

• Demostración de funcionamiento

• Conclusión

• Referencias

A man in a striped shirt stands next to a whiteboard displaying the poster. He is holding a small electronic board (SiPM readout module) in his hands. The poster is titled 'Banco de Pruebas Portable para la Caracterización de SiPMs en Ensayos de Irradiación Basado en FPGA' and contains sections on Introduction, Objectives, Design, Demonstration of Functionality, and Conclusions.

Poster presentado en el congreso. El documento en formato PDF se encuentra disponible en el repositorio del proyecto

Presentador (B. Glecer) exhibiendo el poster

## 6. VALORACIÓN DE DIFICULTADES Y ELEMENTOS FACILITADORES PARA LA CONCRECIÓN DE LA ACTIVIDAD:

### **DIFICULTADES**

1. **Medición de corriente de polarización:** La medición de este valor involucró el diseño de un circuito analógico donde se tuvo que tener muchas consideraciones acerca de la no-idealidad de los componentes.

2. **Portabilidad:** El diseño del PCB presentó desafíos en cuanto a la integración de toda la funcionalidad en ese espacio

3. **Desarrollo FPGA:** Las herramientas y técnicas utilizadas no eran conocidas por el alumno previo al desarrollo del proyecto

4. **Señales de SiPM débiles:** Las señales débiles intrínsecas de un SiPM requieren de electrónica de amplificación de bajo ruido que no resultó trivial su diseño

### **FACILITADORES**

1. **Instrumental y herramientas del LIFEDE y CNEA:** Muchas de las pruebas previo a al desarrollo fueron posibles gracias al equipamiento proporcionado por el laboratorio LIFEDE y CNEA. Además de proporcionar la Red Pitaya, SiPMs y acceso a al ricino de irradiación del RA-1.

2. **Colaboradores alumnos:** Los alumnos Julián Gross y Ari Dayan de la materia Física Electrónica en el segundo cuatrimestre de 2025 colaboraron con la fabricación del gabinete y la impresión en 3D de los soportes internos.

3. **Ayuda docente:** El director de laboratorio Federico Suarez y el docente Matias Hampel fueron de gran ayuda durante el transcurso del proyecto, proporcionando realimentaciones valiosas

4. **Documentación por Pavel Demin:** Los tutoriales y ejemplos de programación de la Red Pitaya fueron de gran ayuda para entender mejor el sistema

## 7. CONCLUSIONES:

En el marco de la Práctica Profesional Supervisada se logró el diseño, construcción y validación de un banco de pruebas para la caracterización de SiPMs orientado a ensayos de tolerancia a radiación. El sistema desarrollado cumple con los objetivos planteados en el documento de inicio: La medición de corriente en oscuridad, el dark-count rate, el espectro single-photoelectron y la ganancia del dispositivo.

El banco de pruebas resultante cumplió el objetivo de ser portable y de bajo costo. El sensado de corriente y tensión, la preamplificación de señales de muy bajo nivel y el procesamiento digital en tiempo real mediante FPGA fueron implementados exitosamente. La utilización de la Red Pitaya permitió concentrar las tareas de adquisición, procesamiento y control en un solo dispositivo, reduciendo la complejidad general del sistema.

Los ensayos realizados durante la campaña de irradiación en el recinto del RA-1 demostraron el correcto funcionamiento del banco de pruebas en un entorno real, permitiendo observar de forma continua la degradación de un SiPM expuesto a radiación de neutrones y gamma, evidenciada por el aumento del ruido en oscuridad, el incremento del consumo de corriente en oscuridad y la modificación del histograma de amplitudes. Estos resultados validan el diseño electrónico y las herramientas de adquisición y procesamiento desarrolladas.

Asimismo, el proyecto permitió abordar desafíos relevantes asociados a la medición de señales débiles y corrientes bajas, al diseño de electrónica analógica de bajo ruido, al desarrollo de lógica digital en FPGA y la integración en un sistema compacto. En este sentido, el trabajo constituyó una experiencia con un alto nivel de aprendizaje, combinando conceptos adquiridos durante la carrera con conocimientos externos que se tuvieron que adquirir específicamente para el desarrollo de este proyecto.

Finalmente, el banco de pruebas desarrollado representa una herramienta útil para futuras campañas de irradiación y estudios de caracterización de SiPMs o otros fotodetectores similares. El proyecto aún presenta la posibilidad de refinamiento y ampliación en sus capacidades. La presentación del trabajo en un congreso nacional refuerza su relevancia académica y técnica, y confirma el valor del desarrollo realizado en el contexto de la ingeniería electrónica aplicada a instrumentación científica.

## 8.BIBLIOGRAFÍA

- [1] STEMlab 125-14 - Red Pitaya. (2021, June 7). <https://redpitaya.com/stemlab-125-14/>

- [2] KiCad EDA. (n.d.). <https://www.kicad.org/>

- [3] JLCPCB. (2020). PCB Prototype & PCB Fabrication Manufacturer - JLCPCB. <https://jlpcb.com/>

- [4] DigiKey Electronics - Electronic Components Distributor. (n.d.). [Www.digikey.com](http://www.digikey.com).

<https://www.digikey.com>

- [5] Red Pitaya Notes. (2025). Github.io. <https://pavel-demin.github.io/red-pitaya-notes>

- [6] Downloads. (2025). AMD. <https://www.xilinx.com/support/download/index.html>

- [7] Analog Devices. (n.d.). LT3482: 90V boost DC/DC converter with APD current monitor (Data sheet No. 3482fa). Analog Devices.

<https://www.analog.com/media/en/technical-documentation/data-sheets/3482fa.pdf>

- [8] Analog Devices, Inc. (1992). *DAC8562: +5 Volt, Parallel Input Complete 12-Bit DAC* (Data Sheet, Rev. A). Analog Devices.

<https://www.analog.com/media/en/technical-documentation/data-sheets/dac8562.pdf>

- [9] Texas Instruments Incorporated. (2025). *OPAx392 precision, low-offset-voltage, low-noise, low-input-bias-current, rail-to-rail I/O, e-trim™ operational amplifiers* (SBOS926I, Rev. March 2025) [Datasheet]. <https://www.ti.com/lit/ds/symlink/opa392.pdf>

- [10] Red Pitaya. (n.d.). *3D\_STEM\_125-14\_v1.0* (3D models) [ZIP file].

[https://downloads.redpitaya.com/doc/3D\\_models/3D\\_STEM\\_125-14\\_v1.0.zip](https://downloads.redpitaya.com/doc/3D_models/3D_STEM_125-14_v1.0.zip)

- [11] Bruno Glecer. (n.d.). *sipm-testbench* (GitHub repository). GitHub.

<https://github.com/brunogle/sipm-testbench>

- [12] Jordanov, V. T., Knoll, G. F., & Pantazis, J. A. (1994). Digital techniques for real-time pulse shaping in radiation measurements. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 353(1), 261–264. [https://doi.org/10.1016/0168-9002\(94\)91652-7](https://doi.org/10.1016/0168-9002(94)91652-7)

- [13] Hamamatsu Photonics K.K. (2015). MPPC® (multi-pixel photon counter) S12571-025, -050, -100C/P (Cat. No. KAPD1042E) [Datasheet].

[https://hamamatsu.su/files/uploads/pdf/3\\_mppc/s12571-025\\_050\\_100\\_c\\_p\\_kapd1042e.pdf](https://hamamatsu.su/files/uploads/pdf/3_mppc/s12571-025_050_100_c_p_kapd1042e.pdf)

- [14] V Congreso Argentino de Técnicas Neutrónicas. (2025). TN|2025 – 18 y 19 de noviembre 2025 (Sitio web de conferencia). Sciencesconf.org.

<https://tn-2025.sciencesconf.org/>